【TC234_通讯QSPI模块】

前言

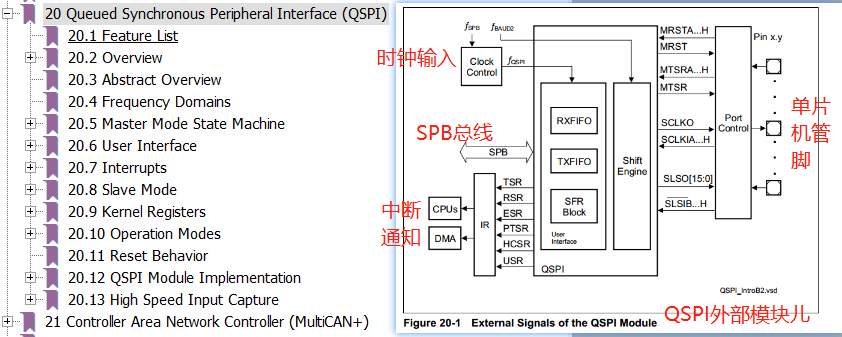

QSPI模块儿(Queued Synchronous Peripheral Interface)章节内容如下图,文章从3个方面实现原理、代码实现、代码分析记录学习过程。

实现原理

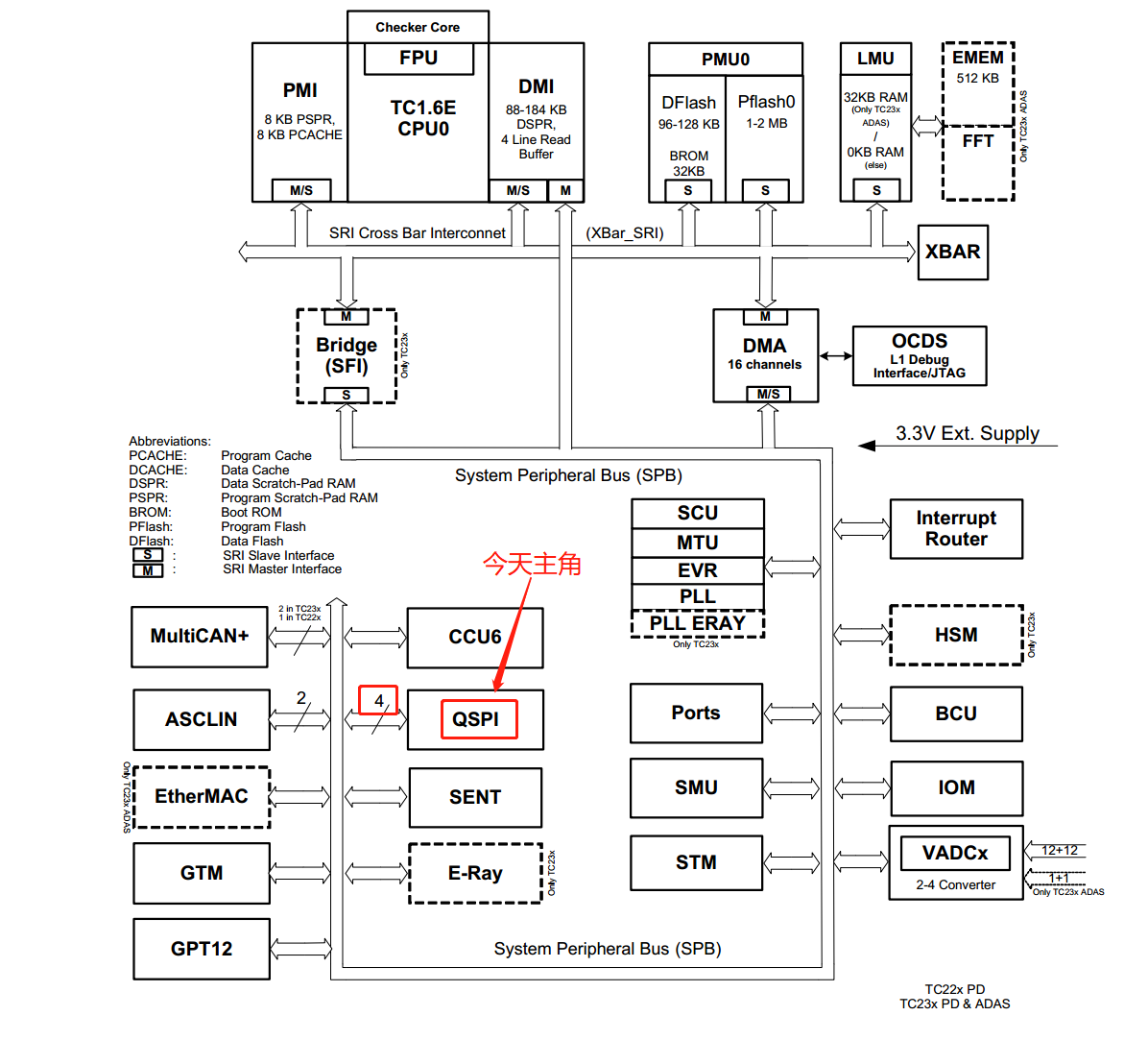

TC234的QSPI模块具有以下特性:

主从模式和全双工通信:QSPI模块支持主从模式,能够实现全双工通信,这意味着数据可以在同一时间内进行发送和接收1。

高速通信:TC234的QSPI接口最高可以达到50 Mbps,这对于单IO的SPI来说是一个非常快的速度2。

FIFO缓冲区:QSPI模块具有4x32bit的Tx和Rx FIFOs,这有助于提高数据处理的效率和稳定性1。

多路片选:模块支持多路片选,每路SPI最多可支持16路片选,这增加了模块的灵活性和可扩展性1。

中断模式:QSPI模块支持FIFO的单点中断模式、ERR中断和PT的(EOF)中断,这有助于更好地管理数据传输过程中的错误和状态1。

数据传输模式:QSPI模块支持多种数据传输模式,包括Short Data模式、Long Data模式、Continuous模式等,这些模式适用于不同的数据传输需求1。

配置灵活性:QSPI模块可以通过配置不同的波特率、延时时间、校验等方式来适应不同的外部设备,这使得模块在工业和汽车应用中非常有用1。

硬件保护:所有嵌入式NVM和SRAM均受ECC保护,这有助于提高数据的可靠性和系统的稳定性3。

多种通信接口:TC234提供了4个QSPI接口,可以配置为4线模式或3线模式,支持多种通信需求2。

这些特性使得TC234的QSPI模块在工业和汽车应用中表现出色,能够满足高可靠性和高性能的需求。

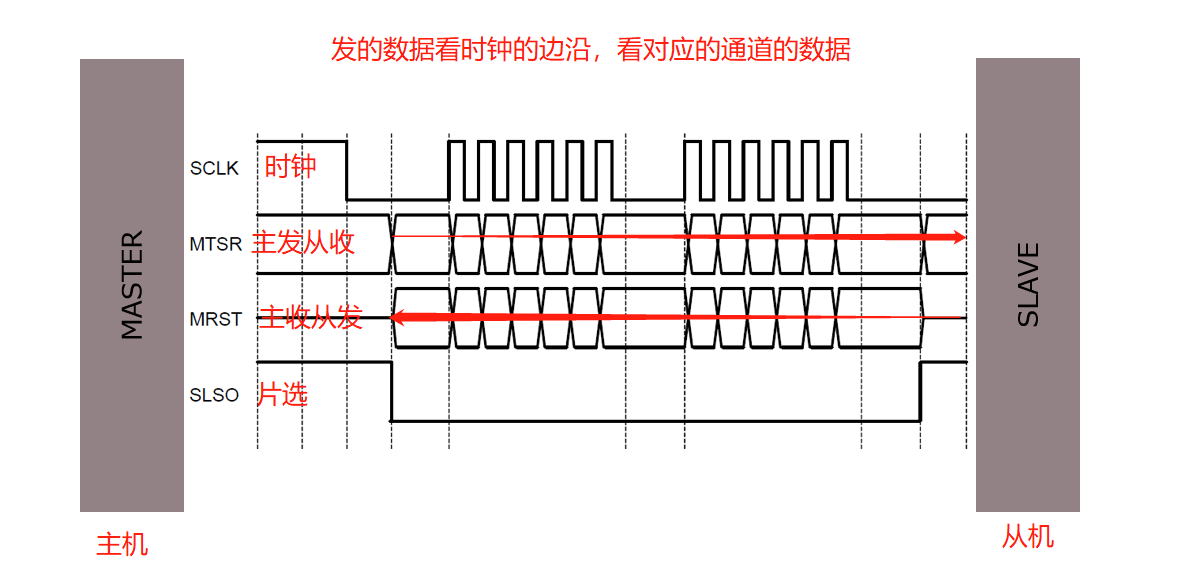

SPI通讯协议原理

SPI(Serial Peripheral Interface)是一种同步串行通信接口,主要应用于短距离、低数据速率的通信,常用于嵌入式系统。

SPI通信的四个重要元素:

主机(Master):初始化通信并控制时钟信号的设备。

从机(Slave):被主机通信的设备。

时钟信号(SCK):主机生成的同步时钟信号,用于同步数据传输。

数据输出(MOSI)和数据输入(MISO):用于主机和从机之间的数据传输。

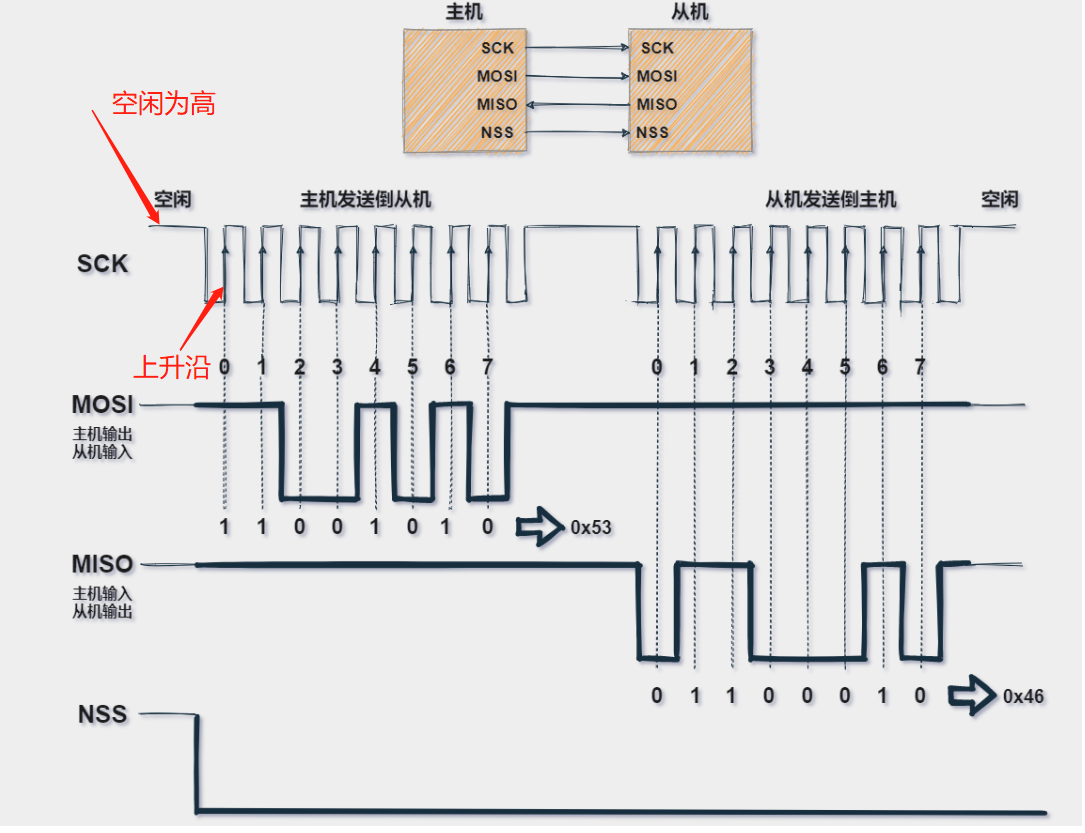

简单举个读数据的例子,参考链接处有更详细的讲解。下图是其中一种模式3(这个模式不用记因为有的仪器模式对应的极性和相位不一样哈哈哈哈),然后简单看一下SPI怎读数据的就可以。

每种模式由时钟极性(CPOL)和时钟相位(CPHA)决定,共有四种模式:

模式0(CPOL=0, CPHA=0):在这种模式下,SCLK在空闲状态下为低电平,数据在SCLK的上升沿进行采样,在下降沿进行传输。

模式1(CPOL=0, CPHA=1):在这种模式下,SCLK在空闲状态下为低电平,数据在SCLK的下降沿进行采样,在上升沿进行传输。

模式2(CPOL=1, CPHA=0):在这种模式下,SCLK在空闲状态下为高电平,数据在SCLK的下降沿进行传输,在上升沿进行采样。

模式3(CPOL=1, CPHA=1):在这种模式下,SCLK在空闲状态下为高电平,数据在SCLK的上升沿进行传输,在下降沿进行采样。

QSPI的主要参数

// Enabled, //1,通道使能

// 3, //2,属于第几个模块

// 2, //3,使用的片选序号(0~7)

// Low, //4,片选有效电平

// 2000000, //5,波特率设置,单位:Hz

// 0, //6,CPOL(Clock Polarity)时钟极性:“0”空闲低“1”空闲高

// 1, //7,CPHA(Clock Phase)时钟相位: “0”第一个边沿 “1”第二个边沿

// MSB, //8,LSB或MSB选择

// 16, //9,命令帧Bits长度(8~4096)

// 500, //10,idle段时间,单位:1ns/bit

// 500, //11,cs到clk段时间,单位:1ns/bit

// 500, //12,clk到cs段时间,单位:1ns/bit

代码实现

代码分析

参考链接

SPI协议详解(图文并茂+超详细)_spi发送和接收过程-CSDN博客

行则将至,道阻且长~