【TC234_TC1.6E核架构】

前言

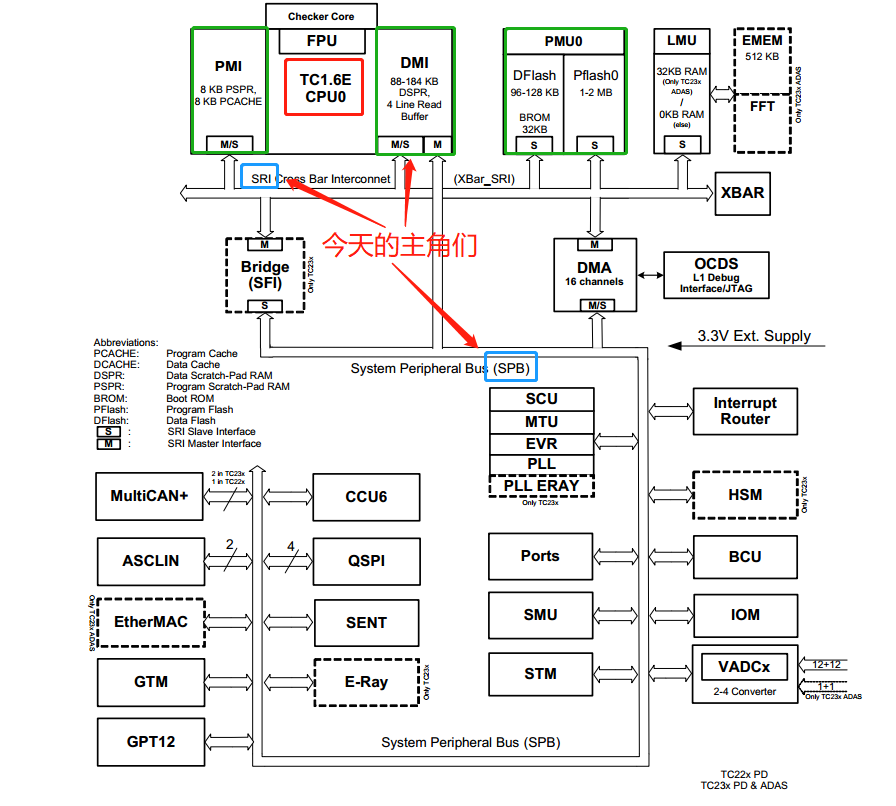

英飞凌AURIX系列有TC1.6E(Efficiency)、TC1.6P(Performance性能)两个核心。文章从多核架构(核心架构、锁步核、SRI资源共享接口、SPB系统外围总线)、存储空间(地址分配、PMU存储单元、PMI程序存储器接口、DMI数据存取器接口)两大部分来记录学习过程。

多核架构(TC387框图)

TC1.6P、TC1.6E核心架构

简称说明:

PMI(Program Memory Interface):程序内存读取接口

DMI(Data Memory Interface):数据内存读取接口

CPS(CPU Slave Interface):外设总线接口

FPU(Floating Point Uint):浮点运算单元

GPR(General Purpose Registers File)通用寄存器包括16个地址寄存器、16数据寄存器(也就是程序的上下文)

Instruction Fetch Uint 指令提取单元

Execution Uint 执行的单元包括整数运算、存储、循环

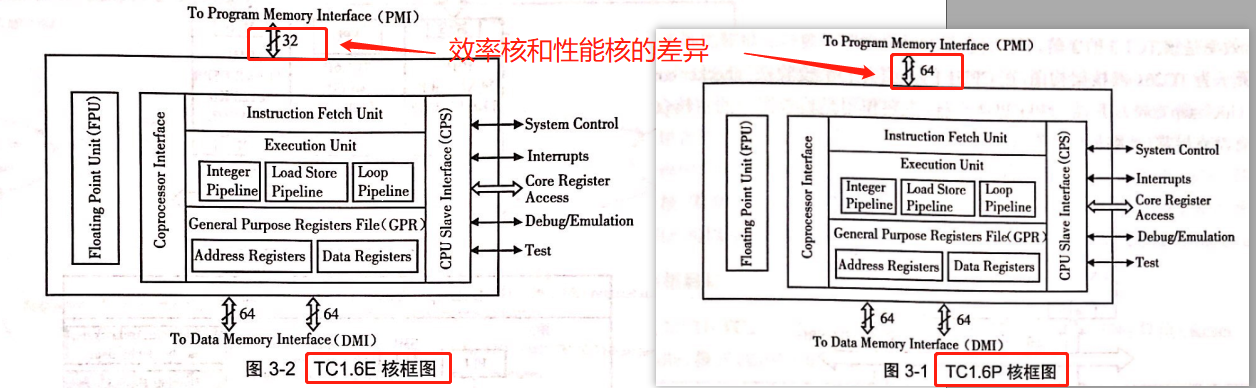

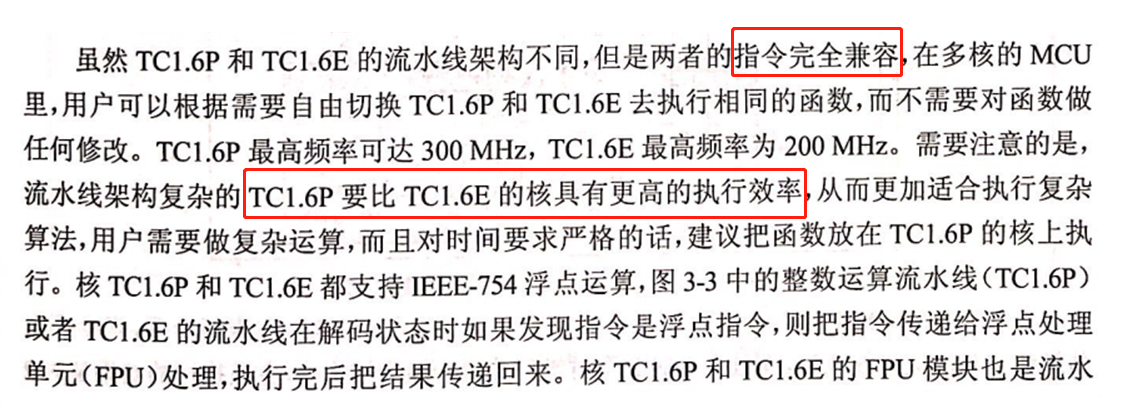

TC1.6P(图3-1)和TC1.6E(图3-2)的核架构仍然采哈佛结构,具有独立的指令接口和数据接口,从而支持高效的数据与指令访问。核TC1.6主要由程序存储区接口、数据存储区接口、取指单元、执行单元(3 个流水线:整数运算、或存储和循环)、浮点处理单元(支持IEEE-754)、通用寄存器组(16个地址寄存A0~A15,16个数据寄存器: DO~D15)、CPU 从接口(中断和系统控制等)组成。

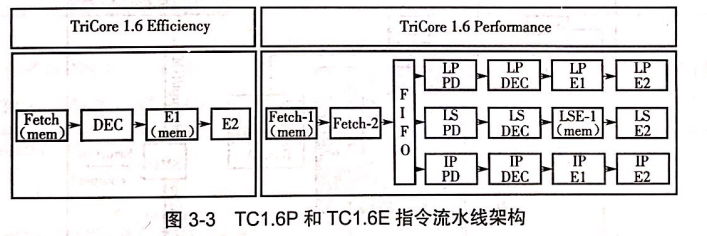

核TC1.6E在框图上和核 TC1.6P 相似,主要区别在于执行单元,TC1.6P 的核有3个流水线(整数运算加载存储和循环),每个流水线有 6 级状态(指令预取 1、指令预取2、预解码、解码、指令执行1、指令执行 2)。TC1.6E 的核有1个流水线(整数算和加载存储实际上在一起),流水线有4级状态(取指、解码、指令执行 1、指令执行2)。

图3-3 所示是TC16P 和TC1.6E指令流水线架构的对比。

锁步核

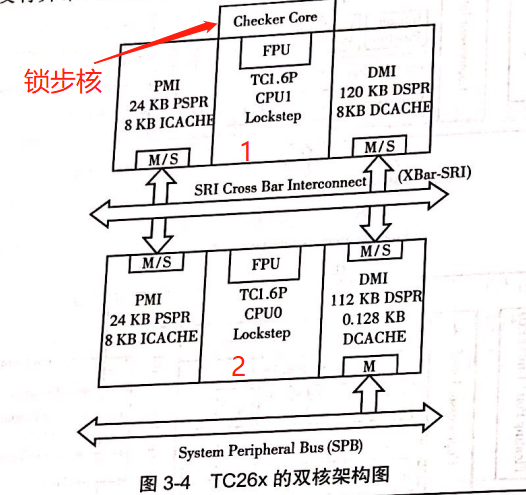

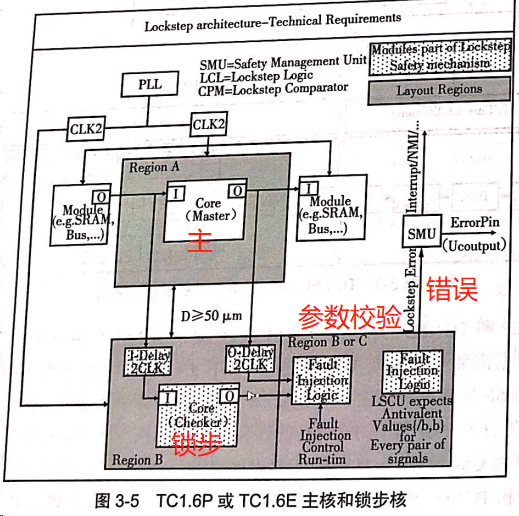

在 CPU1的上面有一个校验(checker core),通也称锁步核(lockstepcore),其结构和 CPU1 一样,要作用是检查图中的主核(CPU1)

执行指令时有没有异常,详细框图如图 3-5 所示。

从核 Checker 和主核 Master 架构完全同,当主核从程序存储区取来指令后,指令不仅传递给自身的流水线执行,而且会延时2个时钟后传递给锁步核执行,主核执行的结果延时2个时钟后送到比较单元与锁步核的执行结果进行对比,如果不相同,会触发Alarm 报警信号给SMU。由于主核和从核在执行相同指令的时间点有 2个时钟的延时,同一流水线上的相同状态 stage 在同一时刻执行不同的指令,从而可以避免主核和从核在相同的干扰下不能正确识别出错误的状况出现,另外主核和从核采用了取反逻辑、数据和指令相反,也有利于提高对执行过程中出现的错误的检出率。MCU 上电时按照BMI(Boot ModeIndex)的设置使能或禁止锁步核,需要注意的是锁步核一旦使能,软件不能关闭锁步核。为了验证锁步核是否正常工作,用户可以注入错误,从而触发 Alarm 警告到 SMU(Safety Management Unit)。

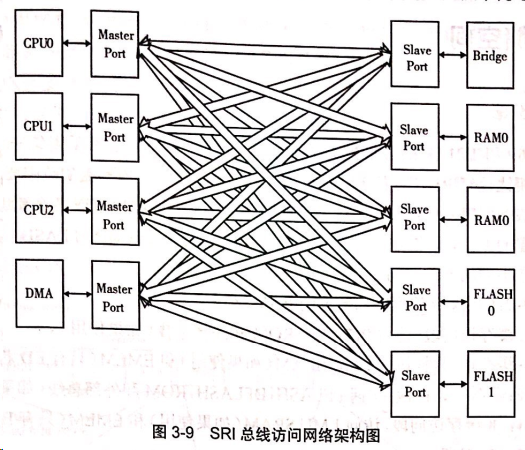

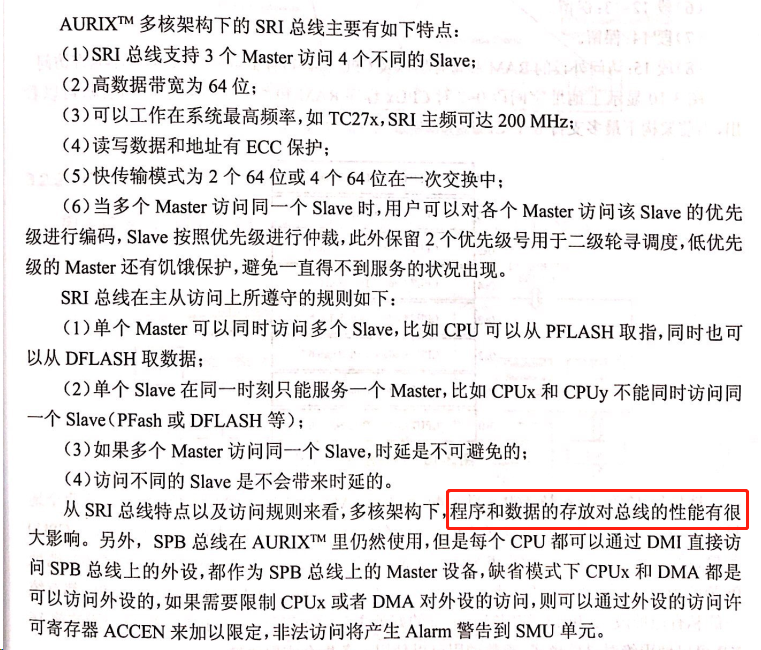

SRI资源共享接口

SPB系统外围总线

参考链接

行则将至,道阻且长~